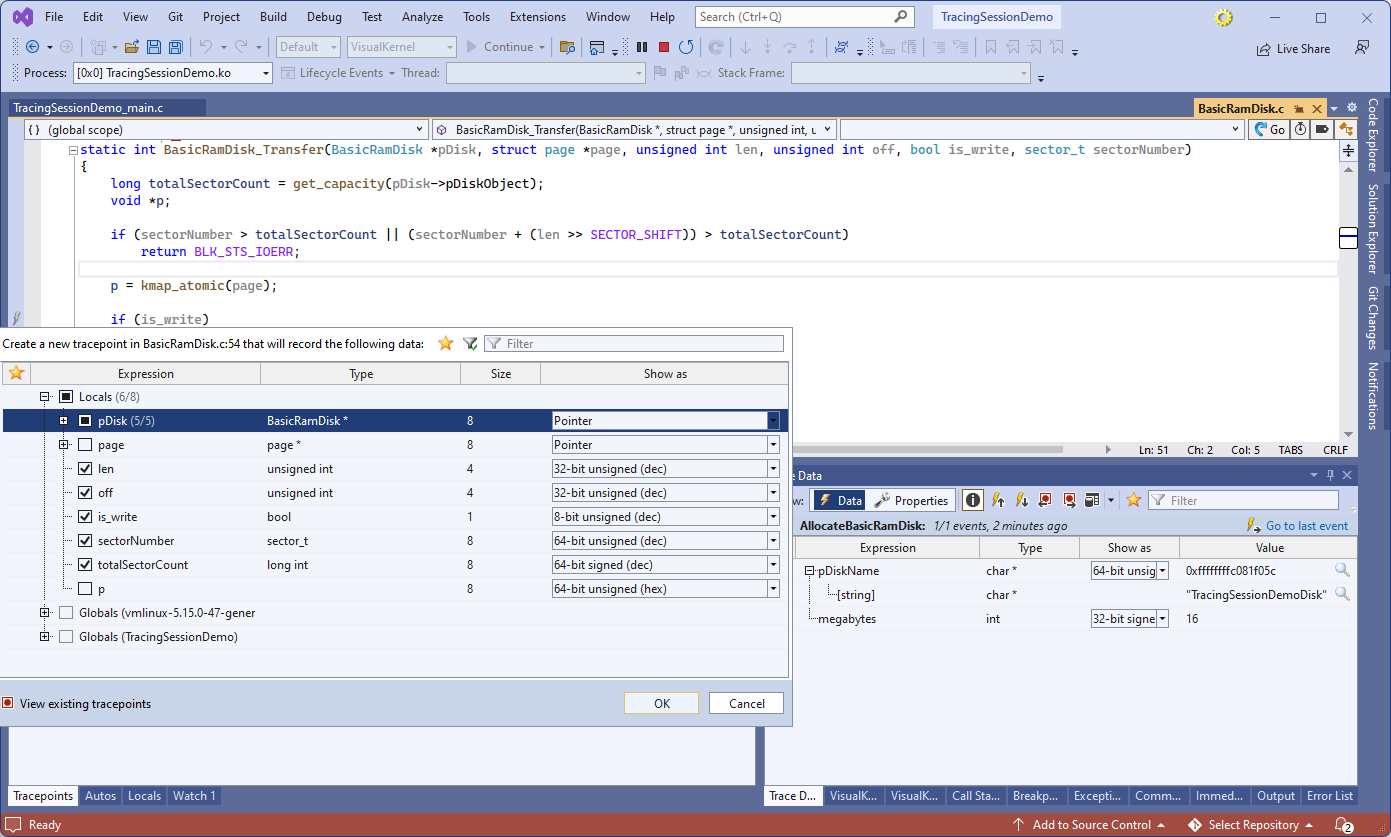

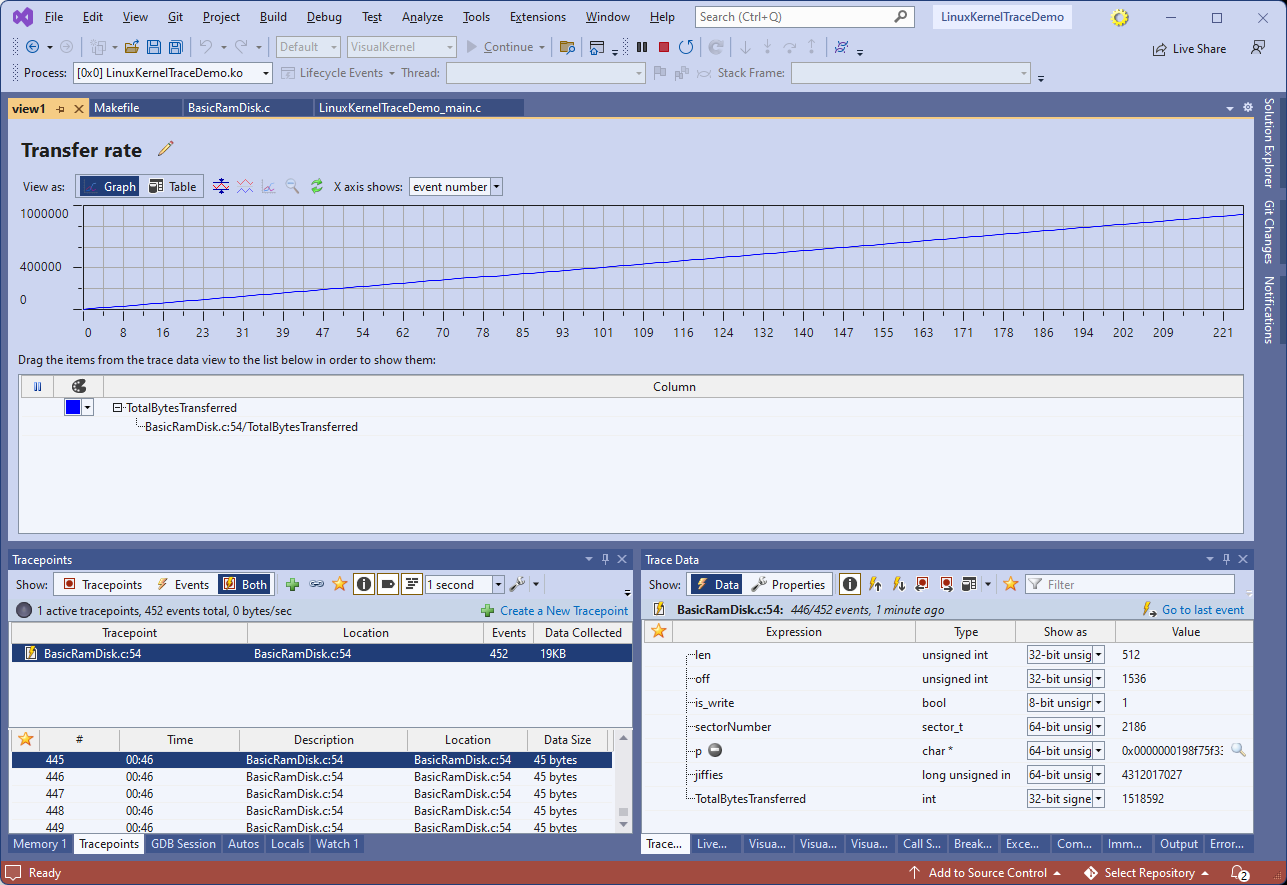

One of the toughest things about debugging embedded systems is that setting a breakpoint isn’t always an option. Sometimes, you don’t know where exactly the problem is until everything crashes. Sometimes, you cannot pause your device for a couple of seconds because it’s continuously talking to other parts of the system. Even if you can, good luck finding that inconsistency among 100 USB packets handled by your device within the past second.

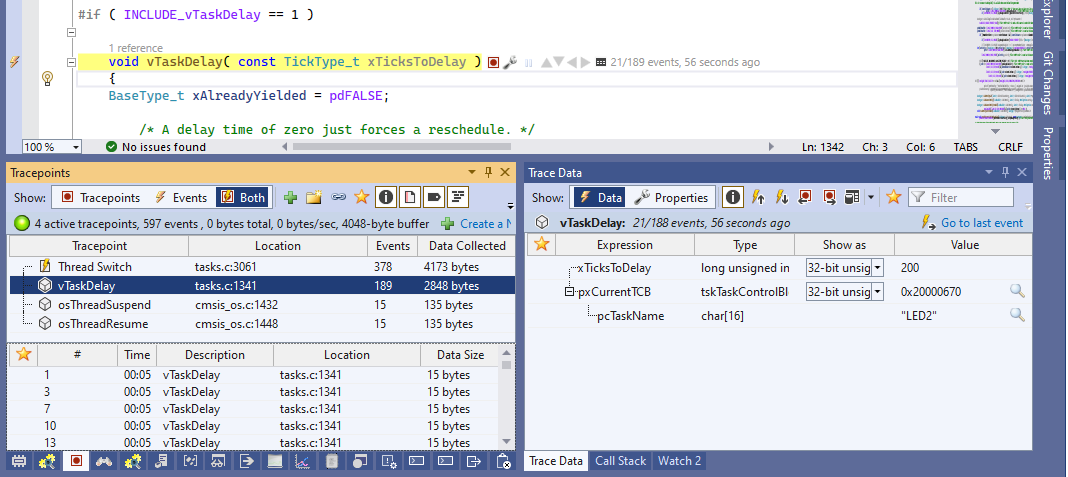

VisualGDB 6.0 fixes this once and for all with the new software-based Live Tracing – a mechanism for setting tracepoints and recording what exactly the application is doing without having to stop it: Continue reading VisualGDB 6.0 – Live Tracing for Embedded Targets

Continue reading VisualGDB 6.0 – Live Tracing for Embedded Targets