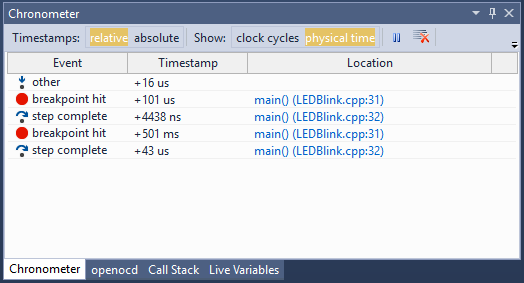

Today we are proud to announce the release of VisualGDB 5.3 Preview 8. This build mainly focuses on stability and usability improvements, such as better integration with Kinetis KSDK 2.x and support for importing Keil projects, however it also introduces a feature that greatly simplifies and reduces the overhead of analyzing precise timing of your embedded code – Chronometer.

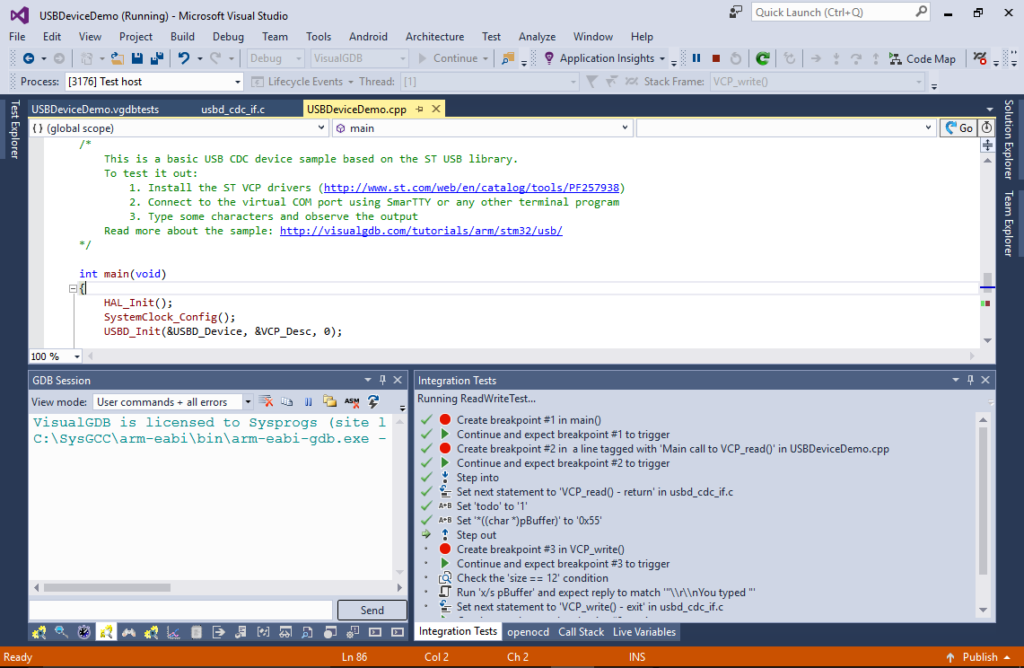

Introducing Embedded Integration Tests

VisualGDB started supporting unit tests in version 5.2. Having out-of-the-box support for CppUTest, GoogleTest and TinyEmbeddedTest, VisualGDB made it easy to check whether every separable component of your system works. However the size overhead and the necessity to create a separate test project makes it hard to use them for testing the behavior of the entire embedded system.

So in VisualGDB 5.3 Preview 7 we introduced a new mechanism called Embedded Integration Tests that does exactly that – lets you conveniently verify the behavior of your firmware without any significant overhead.

VisualGDB 5.3 Preview 6 Released

Today we announce the release of VisualGDB 5.3 Preview 6. It focuses on further improving the usability of the embedded and Linux projects. I will give you an overview of the highlights of this version in this post.

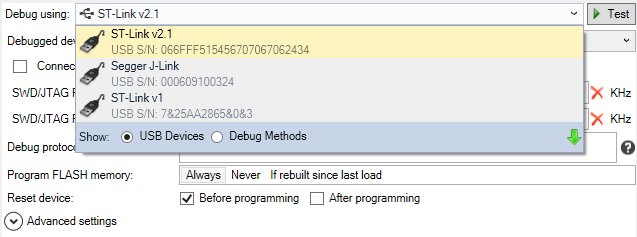

The Updated VisualGDB Embedded Debugging Experience

VisualGDB has a history of supporting embedded devices that has gone through several steps of evolution. The very first VisualGDB version released 5 years ago expected you to know the gdb and OpenOCD command lines, one of the next versions provided convenient GUI for locating OpenOCD scripts and settings that eventually morphed into detecting the settings for common devices and debug adapters, still requiring to go into script editing to support choosing a specific ST-Link instance or turning on the “Connect under reset”.

VisualGDB 5.3 Preview 5 replaces this experience with a much more streamlined (and powerful) UI and I will show you its main highlights in this post.

Continue reading The Updated VisualGDB Embedded Debugging Experience

Introducing the new Team Settings Engine

Since we released the first version of VisualGDB, it has evolved from a basic debugging plugin to a comprehensive extension that helps manage numerous toolchains, packages, build machines, project templates and more. VisualGDB offers GUI for managing those artifacts on the developer machines, however setting up a new development machine from scratch could be annoying due to necessity to setup remote host connections, toolchains, aliases etc.

VisualGDB 5.3 Preview 4 introduces a new mechanism that allows instantly sharing various common settings with other team members – VisualGDB Team Settings. Continue reading Introducing the new Team Settings Engine

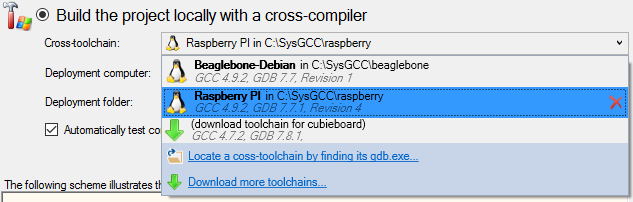

Introducing the New Toolchain Engine

Today we are proud to announce the release of VisualGDB 5.3 Preview 3 that introduces a new improved engine for toolchains and BSPs. The new engine completely decouples project settings from toolchain settings, letting you easily switch between different toolchain options and seamlessly open projects on machines that have different toolchain/BSP installation directories.

Clang IntelliSense Improvements in VisualGDB 5.3 Preview 2

Today we are excited to announce the second preview of VisualGDB 5.3 that introduces several improvements to the Clang IntelliSense engine. In this post I will show you the highlights of the new engine. Continue reading Clang IntelliSense Improvements in VisualGDB 5.3 Preview 2

Introducing the new Advanced CMake Project Subsystem

CMake has been getting increasingly popular over the past years due to its simplicity and integration with the modern IDEs. The recently added CMake Server mode made it even more usable, allowing it to share the precise project structure with different IDEs, but if you wanted to actively edit a large project, you would still inevitably have to edit the CMakeLists.txt files manually, making it less intuitive than working with regular Visual Studio projects.

So we decided to bridge this gap and designed a new VisualGDB CMake Project subsystem that lets Visual Studio open Linux CMake projects and treat them just like the normal Visual C++ projects. Continue reading Introducing the new Advanced CMake Project Subsystem

Extracting mbed build settings for offline builds

ARM Mbed is a powerful embedded framework that supports many modern devices and allows creating complex firmware (like USB devices or Bluetooth LE beacons) using easy high-level C++ API. Although mbed comes with a powerful build system that makes sense of the numerous targets and features, it is optimized for the online compiler, so building the projects offline (and debugging them) could be tricky.

So we decided to make a tool that integrates into the Python-based mbed build system, polls it for supported targets, features and libraries and stores the recovered information in a structured XML file that can be used to create Visual Studio projects for various mbed targets. Continue reading Extracting mbed build settings for offline builds

Announcing mbed 5.2 support

Today we are proud to announce full mbed 5.4.2 support in VisualGDB. It comes with a significantly improved integration level compared to the previous beta package:

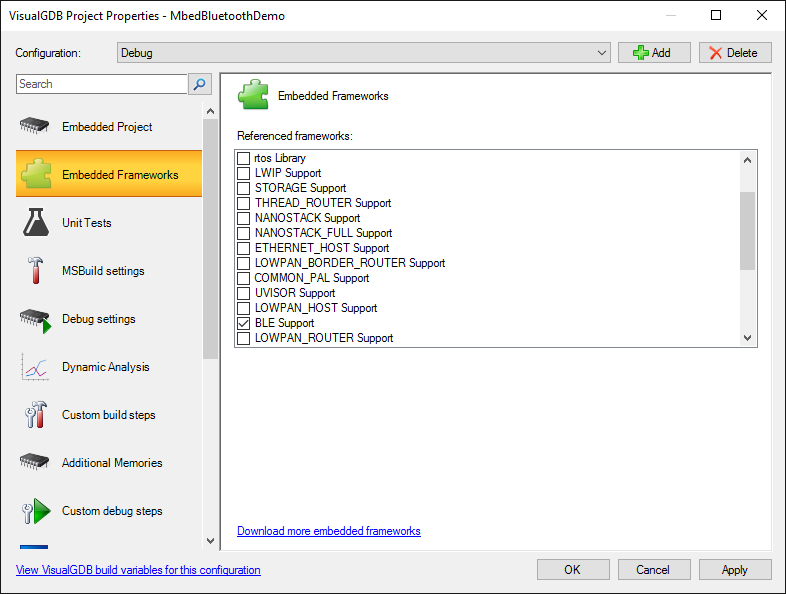

- Features like Bluetooth LE area can now be easily enabled via the Embedded Frameworks page of VisualGDB Project Properties:

- Softdevices and bootloaders for Nordic nRF5x devices are now seamlessly integrated into the build process.

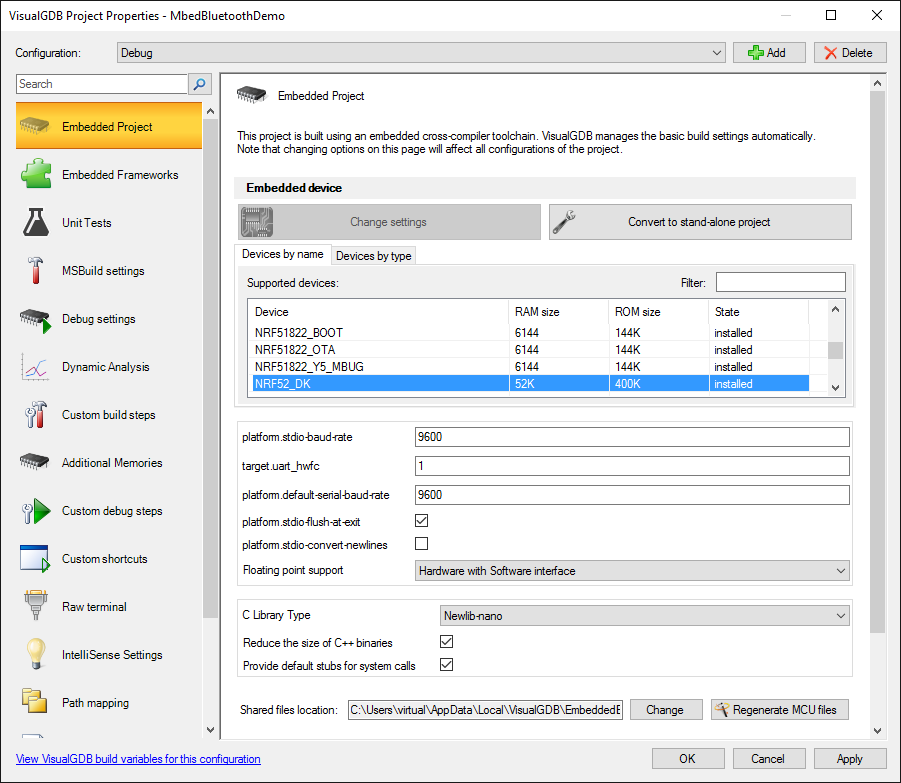

- Various configurable properties (like the default baud rate) are no longer hardcoded and can be conveniently edited via VisualGDB GUI:

- The codebase is updated to the latest 5.4.2 release.

- We have also added an example for Nordic nRF5x UART-over-Bluetooth LE that works out-of-the-box.

You can download the new mbed package via Tools->VisualGDB Package Manager->Updates.